|

Vitis 2022.2 主要增強特性

作者:吳昊( Eddie Wu )/ AMD Vitis 統一軟件平台產品營銷經理

Vitis™ 統一軟體平台 2022.2 版已正式發布。主要增強特性包括下列內容:

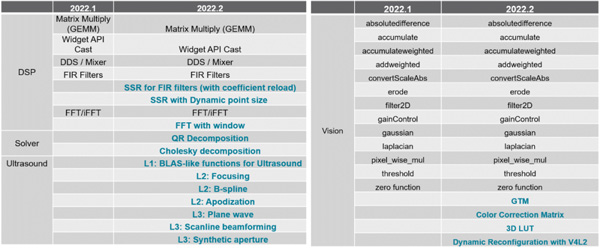

為 Versal AI 引擎陣列提供新的 Vitis 庫功能

• DSP 庫功能 – 增強特性

• 求解器庫功能

• 視覺庫功能

• 超聲庫功能

針對 Versal 器件的設計流程增強

• 控制內核在 AI 引擎陣列中的相對佈局,從而提升性能,提高利用率

• 強化面向 Versal® ACAP 設計的配置與調試功能,包括死鎖檢測、較大佈線數據採集、

RTL/Python 測試平台支持

• Vitis 集成設計環境下的異構設計的新仿真選項

在 Vitis 軟體平台 2022.2 版中,Vitis 庫經過強化,能支持更多用於 AI 引擎陣列的功能

1- 通過係數再加載功能和動態點大小,DSP 庫現可支持超高采樣率( SSR )FIR 濾波器。

在指向 AI 引擎陣列的 FFT 功能中,新增 FFT 窗口化元素

2- 對於求解器庫,為 AI 引擎陣列新增兩個矩陣分解功能,分別是 QR 分解和喬里斯基

( Cholesky )分解。這兩種是得到廣泛運用的矩陣運算

3- Vitis 視覺庫為 AI 引擎陣列新增四項功能:全局色調映射( GTM )、色彩校正矩陣、

3D 查找表和符合 V4L2 的動態重配置。

4- 2022.2 版還提供新的超聲庫,其中包括 L1 級到 L3 級功能。

• L1 例程為超聲波提供類似基本線性代數子程序( BLAS )的功能。

• L2 例程為聚焦、變跡和 b 樣條等功能提供 AI 引擎圖。

• L3 例程提供合成孔徑、平面波和掃描線波束成型等超聲子系統。

2022.1 版和 2022.2 版為 AI 引擎提供的 Vitis 庫的更詳細介紹請見下文。

Versal ACAP 設計流程強化

AI 引擎編譯器

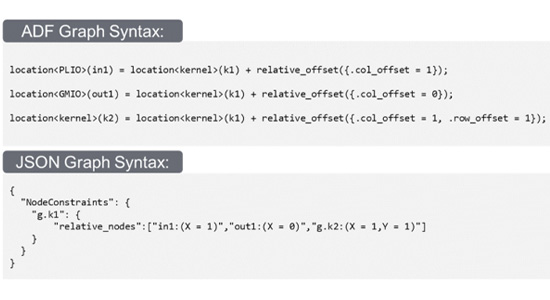

在這個新版本中,AI 引擎相對約束提供了在 AI 引擎內控制內核相對佈局的途徑。這有利於用戶從 AI 引擎陣列獲得更高性能和更充分的利用率。可以將約束定義為自適應數據流程( ADF )圖格式和 JavaScript 對象標記( JSON )格式。

ADF 和 JSON 圖形語法例如下所示:

有關 Vitis 工具仿真與分析的新特性

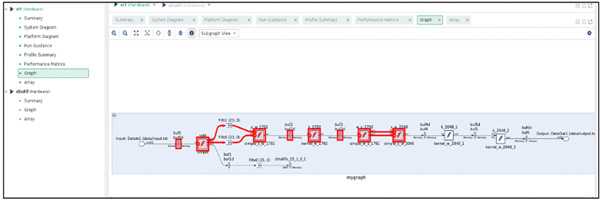

1.採用Vitis 分析器配置、調試和分析 Al 引擎

在2022.2版中,可以在 vitis 分析器中的硬體模擬階段分析 Al 引擎的狀態,為調試提供幫助。而在2022.2版以前,用戶必須在硬體內構建設計,才能開展同樣的分析。這項特性允許用戶在構建硬體前開展配置,加快迭代速度,同時幫助縮短設計週期。

從 2022.1版起,通過 Linux 上的xbutil 和 XRT,就可以啟用死鎖檢測。現在使用賽靈思系統調試器 (XSDB)也支持同樣的特性。這對裸機用戶有所幫助。可以生成與xbutil生成的文件等效的JSON 文件。這個文件可以導入Vitis 分析器查看。

死鎖檢測流程如下所示

這項新特性將對XRT的支持擴展到對基於 Al引擎的XSDB 流程的支援。

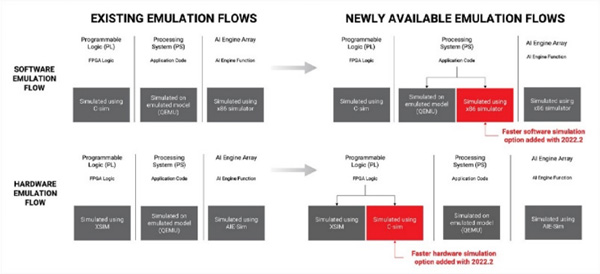

2.支援在x86主機上用 PS 應用開展軟體模擬

除了在嵌入式平台上的QEMU,現在用戶可以在 x86仿真器上通過編譯和運行處理系統(PS)應用來模擬軟體,加快軟體模擬的速度。這項功能無需創建 SD 卡鏡像,也無需在QEMU中引導 Linux,從而避免相關開銷,加快周轉時問。用戶可以使用 XRT 控制加速內核,自己則專注於高級功能模型。使用此功能前,必須在主機上安裝賽靈思運行時庫(XRT)。

3.除了 RTL以外,還可以使用 SystemC 功能模型進行硬體模擬

與RTL相比, SystemC 功能模型能加快編譯速度,縮短執行時問。此外,用戶也可以搭配使用C 內核和 RTL內核來調試 RTL塊。在2022.2版中,支持C/C++ 內核、基於AXI4-Memory Map 的內核和基於 AXI4-Stream 的內核。

新的仿真選項進一步豐富了用戶可用的功能仿真流程,如下所示。這些新的仿真流程主要用於協助實現快速功能仿真。

4.使用簡單的RTL測試平台或基於 Python 腳本的流量生成器為仿真 Al 引擎內核提供支援

這項特性允許用戶將 RTL 測試平台重複用作流量生成器(TG) 或使用 Python 創建流量生成器。這樣做無需完整平台就可以單獨驗證內核。

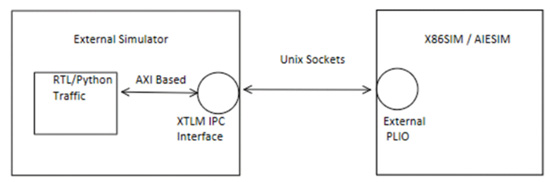

RTL仿真器使用上述測試平台, x86SIM/AIESIM 負責仿真 C或 Al 引擎內核代碼,利用 Unix 套接宇和 XTLM IPC接口在兩個進程間建立通信,如下所示。

通過 Vitis 軟體平台 2022.2 版,我們現在支援 Python、VHDL、Verilog 和基於 SystemVerilog 的流量生成器。

即刻下載 Vitis 統一軟體平台 2022.2 版,了解最新特性與全新功能吧!

閱讀原文

|