|

Versal ACAP 硬體、IP 和平台開發方法指南

賽靈思 Versal® 自適應計算加速平台( ACAP )設計方法論是旨在幫助精簡 Versal 器件設計進程的一整套最佳實踐。鑑於這些設計的規模與復雜性,因此必須通過執行特定步驟與設計任務才能確保設計每個階段都能成功完成。建議您遵循這些步驟和最佳實踐進行操作,這將有助於您以盡可能最快且最高效的方式實現期望的設計目標。

• 系統設計類型

Versal ACAP 屬於異構計算平台,具有多個計算引擎。在 Versal 上可映射各種應用, 包括對無線系統、機器學習推斷和影片處理算法進行信號處理。除了多個計算引擎外,Versal 還可使用高速串行 I/O、NoC、DDR4/LPDDR4 儲存器控制器和多重速率以太網媒體訪問控制器( MRMAC )來提供超高系統帶寬。

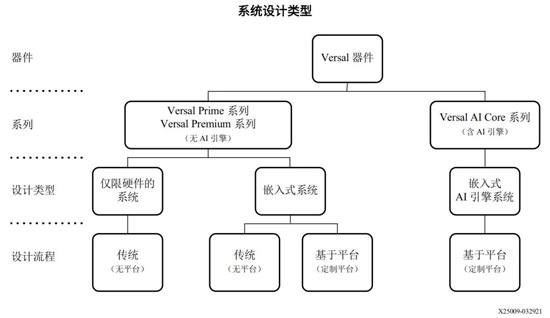

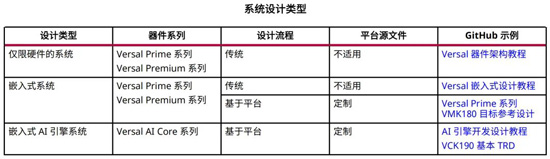

針對 Versal 器件中的Versal Prime、Versal Premium 和 Versal AI Core 系列,下圖顯示了每種系列所支持的不同系統設計類型和設計流程。

下表顯示了每種 Versal 器件系列所支持的系統設計類型和設計流程。如該表中所示,大部分設計流程都以構建平台為基礎。

您可以訪問賽靈思 GitHub 獲取更多範例,這些範例定期更新。

• Versal ACAP 的設計流程

- 傳統設計流程(無平台)

在傳統設計流程中,系統的整個 PL 部分都是在單個 Vivado 工程中定義的。該工程必須包括 Versal 基礎硬體 IP 塊,以及工程所需的任何其它定制 RTL 和 IP 塊。

設計源文件將添加到 Vivado 工具中,並通過 Vivado 實現流程進行編譯。如果系統僅包含 PL 組件,那麼可使用 Vivado 工具來生成可編程器件鏡像( PDI ),以便對 Versal 器件進行編程。如果系統還包含嵌入式軟體內容,那麼將在從 Vivado 工具導出的固定硬體設計上的 Vitis 環境中開發軟體應用。此流程類似於用於 Zynq UltraScale+ MPSoC 的傳統流程。

- 基於平台的設計流程(定制平台)

在基於平台的設計流程中,系統分為 2 個不同元件,即平台和處理器系統。該平台是一種正規化的設計資源,包含用於構建和集成完整工作系統的 Versal 基礎硬體 IP 塊和軟體功能編。

該平台的硬體部分是一個專用 Vivado 工程,其中包含最少的必需硬體 IP 塊。將軟體組件與硬體封裝在一起以創建定制平台。處理器系統由實現系統主要功能的 PS、PL 和可選的 AI 引擎功能組成。可以使用 Vivado 工具或 Vitis 環境創建這些不同的元件。然後使用 Vitis 環境將這些元件集成到平台中。該流程促進了系統不同元件的並行開發,並加快了異構系統的集成進程。 Versal ACAP 支持 2 種設計流程:傳統設計流程和基於平台的設計流程。要充分利用 Versal ACAP 資源,重要的是選擇正確的設計流程。下表顯示了根據設計類型和目標器件系列所使用的設計流程。

• 了解 Versal ACAP 設計方法論的概念

從設計之初即採用正確方法,從早期階段開始對設計目標(包括 IP 選擇和配置、塊連接、RTL、時鐘、I/O 接口和 PCB 管腳分配)給予足夠的重視,對於確保設計成功都至關重要。在每個設計階段中務必正確定義和確認設計,這有助於緩解在子系統和完全集成的系統的實現階段中出現的時序收斂、性能收斂和功耗使用問題。

- 創建和實現硬體設計

完成器件 I/O 管腳分配、PCB 佈局規劃並決定使用模型後,即可開始創建設計。設計創建包括:

- 規劃設計的層級

- 識別要在設計中使用和定制的 IP 核

- 例化 IP 目錄中不可用的特殊互連或功能所需的 RTL 模組

- 創建時序約束、功耗約束和物理約束

- 指定綜合與實現階段所使用的其它約束、屬性及其它元件

創建設計時,主要的考慮要素包括:

- 實現所需的功能

- 按期望的頻率運行

- 按期望的可靠程度運行

- 符合矽片資源和功耗預算要求

在此階段做出的決策將影響最終產品。在這一階段的錯誤決策會導致後續階段問題層出不窮,進而造成整個設計週期中不斷返工。在此過程中儘早花時間詳細規劃設計有助於達成設計目標並最大限度縮短實驗室中的調試時間。

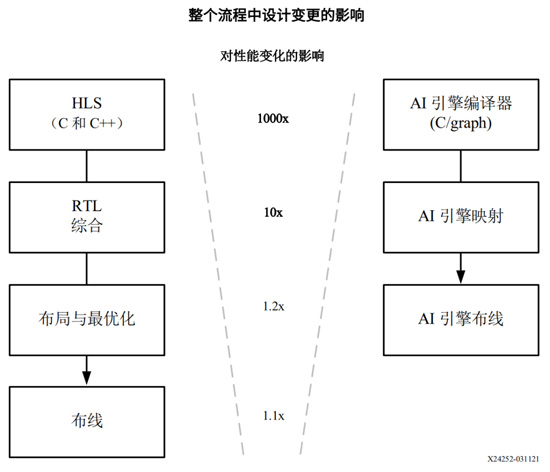

- 在開發週期早期最大限度擴大影響

如下圖所示,設計流程的早期階段(C、C++ 和 RTL 綜合)對於設計性能、密度和功耗的影響遠超後期實現階段的影響。因此,如果設計不滿足時序、時延或功耗目標,賽靈思建議您重新評估綜合階段(包括 C、C++、HDL 和約束),而不是僅在實現階段通過迭代來尋找解決方案。

- 在每個設計階段進行確認

Versal ACAP 設計方法強調對設計預算(例如:面積、功耗、時延和時序)進行監控以及儘早採取如下措施更正設計的重要性:

- 盡可能多加利用 Versal ACAP 集成塊,使用片上網絡 (NoC) 實現高帶寬連接並在模塊框圖級別確認設計性能

- 利用賽靈思模板創建最佳 RTL 結構,並在執行細化後進行綜合前採用方法 DRC 來確認 RTL

- 在綜合後開展時序分析

- 通過運行非關聯綜合和實現來確認每個主要 PL IP 或模組框圖的時序收斂可行性

- 繼續執行下一個設計階段前採用正確的約束滿足時序要求

- 使用設計方法論 DRC

Vivado Design Suite 包含一組方法論相關 DRC,可供您使用 report_methodology Tcl 命令來運行。此命令針對以下每個設計階段都具有相應的規則:

- 在綜合前,在細化 RTL 設計中用於確認 RTL 結構

- 在綜合後,用於確認網表和約束

- 在實現後,用於確認約束和時序相關問題

除了上述關於 Versal ACAP 設計方法論的基本闡述,本指南還包含 8 大主題的高層次信息、設計指南和設計決策利弊取捨, 包括設計規劃、使用塊設計來創建設計、使用 RTL 創建設計、使用 Vitis HLS 創建設計、I/O 管腳分配設計流程、設計約束、設計實現、Vitis 環境嵌入式平台創建方法。

如需查看完整版指南,請點擊連結下載。

閱讀原文

|