|

MicroZed专栏:统一软件平台 Vitis 示例应用详解

编者注:本内容转载自MicroZed 发展历程记录,得到作者和 Hackster.io的许可。

上个星期我们完成了用于 Ultra96 的 Vitis 加速平台的创建工作,并为讲解开发流程创建了一个示例应用。

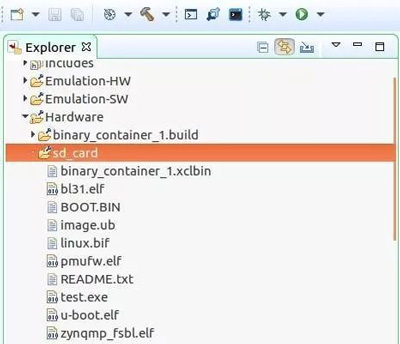

创建的示例应用是一个相当简单的向量加法。编译完成后,Vitis 将运行应用所需的所有文件提供在硬件构建结构下的 sd_card 目录中。

在这个目录中,用户将会看到加载到可编程逻辑中的 boot.bin、内核镜像、向量加法应用和二进制容器,以及我们在硬件上运行示例应用所需的一切。

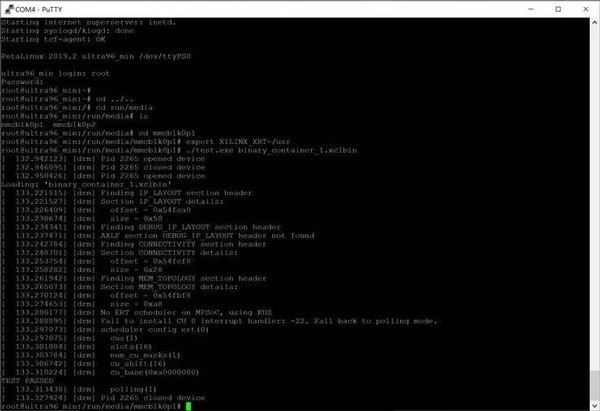

应用本身的运行十分简单。首先是从 SD_Card 目录将文件复制到 SD 卡,然后启动 Ultra96 V2。

图文:SD 卡内容

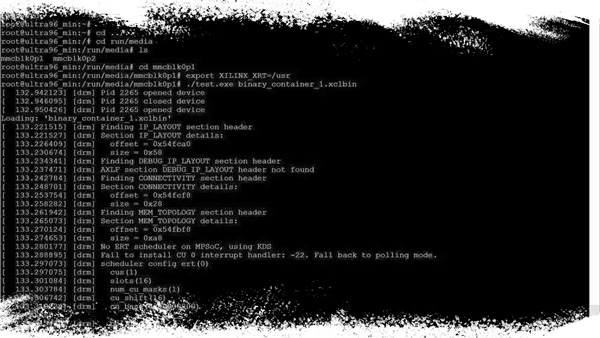

在 Ultra96 成功启动后,我们需要更改目录,才能访问 SD 卡上的文件,以运行示例应用。

将目录更改为如下路径:

现在,我们在正确的目录下,在运行示例应用前,我们需要导出赛灵思运行时的位置。

要运行示例应用,我们接下来只需将程序名称定义为 argv0 并提供 XCLBIN 的名称。

设置并运行向量加法示例

图文:设置并运行向量加法示例

下面我们略为详细地了解一下示例应用的构成。

该示例应用由两个源文件构成:

• vadd.cpp — 包含主机应用,运行在 MPSoC 中的 Arm Cortex A53 核心上。

• krnl_vadd.cpp — 包含可在可编程逻辑中实现的内核。内核使用高层次综合(HLS)实现。

主机应用

主机应用的作用是配置内核,并对内核进行生命周期管理。

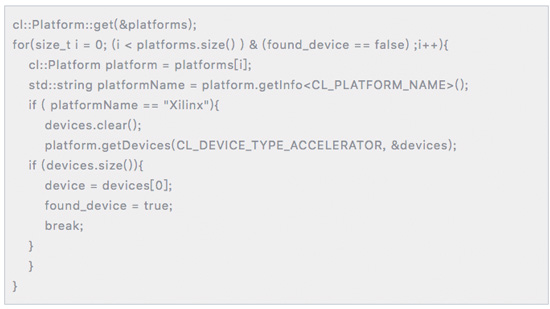

生命周期管理的第一步是确保找到平台与器件:

在完成平台与器件的定位后,接下来是加载 XCLBIN 文件。

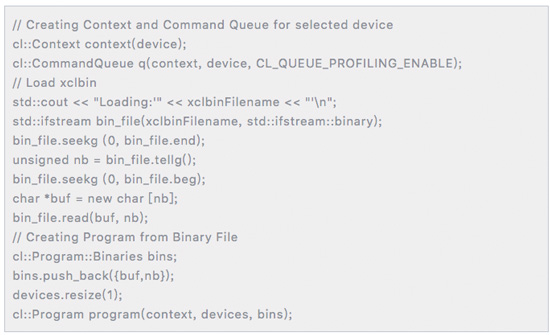

这个阶段的第一步是为目标器件创建 OpenCL 环境并建立命令队列。命令队列有助于实现主机与器件之间的通信。这样主机就能向 OpenCL 器件发布需要执行的命令。

命令队列创建完成后,下一步是加载 XCLBIN 文件。

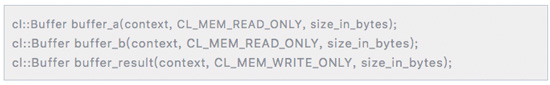

使用 OpenCL 存储模型与内核接口连接。针对器件定义指令,如 buffer_a 和 buffer_b 对内核只读,buffer_result 对内核只写。

这些缓存在全局存储器内进行分配。如果不太熟悉,OpenCL 存储器的结构组成如下:

• 主机存储器 — 仅主机能够访问。

• 全局存储器 — 主机和内核均能访问,是主机和内核间传输数据的主要媒介。

• 恒定全局存储器 — 主机和内核均能访问。但仅有主机能读写,内核仅为只读。

• 本地存储器 — 内核用于计算与存储,主机不能直接访问。

• 专用存储器 — 供内核内部的任务使用,其他任务不能访问该存储区。也不支持主机直接访问。

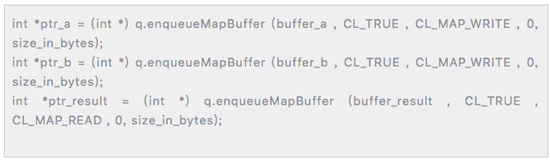

缓存创建完成后,需要对它们进行映射,以便主机应用访问缓存。

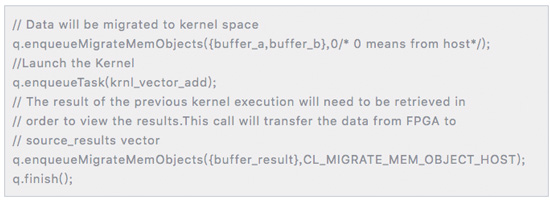

最后在输入数据设置完毕后,我们就可以运行内核。要运行内核,我们需要将输入数据传递给缓存,启动内核,然后从缓存传递出输出数据。

在内核运行完成后,执行工作的下一步是清理软件,释放分配的缓存。

内核实现方案

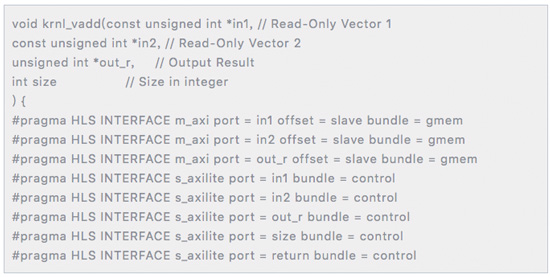

仔细查看内核实现方案,您会发现它与正常的高层次综合设计非常相似。

首先要注意的是接口。内核有四路输入,其中两个是输入向量、一个是结果向量、还有一个输入定义的是待处理的向量数量。

定义输入和输出向量数据的目的是方便实现使用 HLS INTERFACE 编译指示的 AXI 存储器映射端口等,同时对 IP 块控制与向量大小进行配置,以实现在 AXI Lite 接口内。

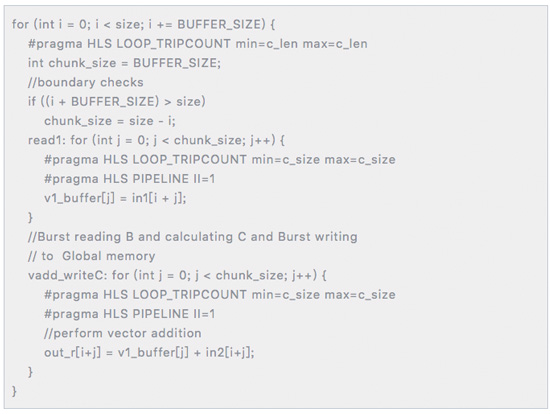

代码主体相当简单,使用嵌套for循环读取数据输入,完成相加并写回结果。

为了在可编程逻辑中优化内核的性能,这些循环被流水线化,让初始间距为 1。也就是处理新输入数据需等待一个时钟周期。

现在我们已经了解了平台的创建过程,并知晓了主机和内核源代码的相关内容,我们需要进一步了解 Vitis 流程,才能创建属于我们自己的应用。

接下来我们将向您介绍如何为各种应用创建 Vitis 加速应用,因为我们已经了解到创建工作有多么简单!

如您对本项目感兴趣,需要查看我的 FPGA/SoC 项目,获取代码,访问 MicroZed 发展历程记录档案,其中有 300 多篇有关 FPGA/Zynq/Zynq MpSoC 的文章

阅读原文

|