| |

嵌入式視覺開發難不難?過來人會告訴你:難!

試想一下,在一個性能受限的嵌入式架構中去跑複雜的視覺處理演算法,還要平衡功耗、尺寸、成本、開發週期等因素,確實不容易。如果你面對的是工業或汽車這種對即時性和可靠性要求較高的場合,視覺處理要快又準,容不得半點閃失。現在人工智慧(AI)時代來了,機器學習是不是也應該相應調整?所以,嵌入式視覺開發者備感壓力。

不過,總是有人琢磨“如何將複雜的事情變得簡單”。在嵌入式視覺開發這件事上,如何為開發者“減負”,已經有了許多好方案擺在我們面前了。

我們先從硬體上來看。單一處理器架構當然更容易上手,但是開發者總免不了要在性能和靈活性、可擴展性上做折衷。直到賽靈思推出了Zynq這種全新架構的FPGA SoC器件,大家才眼前一亮。Zynq是一種異構處理器,內部既包含嵌入式處理器(PS),也有可程式設計邏輯電路(PL)。

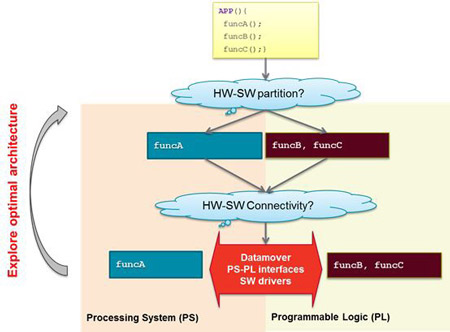

嵌入式視覺開發者可以根據需要將計算任務在兩個系統間進行分配,十分靈活;將高性能的視覺處理功能放在PL上做加速,這自然比用通用CPU處理更高效。由於PL是硬體可程式設計的,所以開發者可以複用成熟的IP,也可以根據演算法編寫自己的定制化IP,實現與眾不同視覺處理效果。

為了更好地支援高性能視覺處理的應用開發,賽靈思特別推出了Zynq Ultrascale+ MPSoC,與上一代Zynq相比,該器件提升了性能,同時為了應對即時性視覺處理做了專門的優化。我們看看Zynq Ultrascale+ MPSoC的核心資源配置,就明白了:

• 四個ARM Cortex-A53 CPU,算力不俗,可以支援功能複雜的OS,如Linux。

• 兩個ARM Cortex R5F即時處理器(RPU),可工作在鎖步和獨立運行模式,鎖步模式可用于安全性要求嚴苛的場合。

• 一個Mali-400圖形處理器,用於2D/3D圖形顯示,可提供高品質的視頻顯示輸出。

不誇張地說,Zynq Ultrascale+ MPSoC就是一顆“為嵌入式視覺”而生的器件,豐富的硬體資源能夠讓開發者達到事半功倍的目的。

圖1,Zynq Ultrascale+ MPSoC將嵌入式視覺作為其主攻應用市場(圖片來源:賽靈思)

硬體架構能夠滿足要求了,但這並不意味著就能玩轉嵌入式視頻開發。以往在開發者心中,想和FPGA打交道,要學會要用專門的硬體描述語言寫HDL代碼,這並不容易,更何況現在面對的Zynq Ultrascale+ MPSoC是一個更複雜的FPGA+CPU的“異構”系統。

這個顧慮,賽靈思早已經料到了,所以他們在推出Zynq之後,也開發出了一個“軟體定義”的工具套件,讓FPGA SoC的開發變得更容易,這就是SDSoC。

對於SDSoC比較通俗的理解就是,它將FPGA SoC所需的開發工具和資源庫整合在一個統一的開發環境中,讓以往需要由系統架構、硬體設計、軟體發展等不同團隊協調合作、反復反覆運算才能完成的複雜設計開發流程,以更為自動化的方式得以實現,簡化了工作,提高了效率。

SDSoC的核心願景就是:讓更多只有很少或根本沒有FPGA設計經驗的研發人員,無需寫一行RTL代碼,就可以直接使用高級程式設計語言程式設計,體驗到可程式設計硬體的的強大能力,並且可以與通用處理器系統一起協同工作。就嵌入式視覺開發而言,開發者使用SDSoC後,可以將更多的時間和精力從繁複的底層開發工作中解放出來,去考慮演算法的優化這類可以給產品帶來更多差異化和附加值的高層次、系統級的問題。

圖2,SDSoC典型開發流程(圖片來源:賽靈思)

可見,SDSoC的出現讓基於Zynq Ultrascale+ MPSoC這類嵌入式視覺硬體平臺的開發效率大為提升。但是,你別以為這就大功告成了。市場的發展會不斷給你提出新的需求,比如說如果今天你還沒有考慮為嵌入式視覺系統加入機器學習功能,明天你的產品可能就出局了。

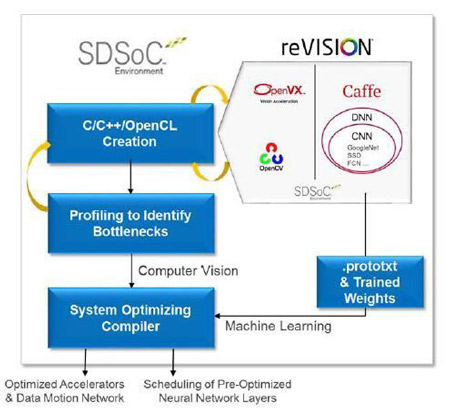

想要在設計上“追新”,傳統的視覺處理設計思路就要改變——開發者要從費時費力的自己做HDL程式設計優化,轉向充分利用現有的成熟、經過驗證的IP資源,通過軟體定義的方式獲得所需的視覺加速性能。賽靈思的reVISION堆疊就是一個將實現新思路所需的所有要素整合在一起的系統環境。

reVISION堆疊包括豐富的平臺、演算法和應用開發資源,支援最流行的神經網路,如AlexNet、GoogLeNet、SqueezeNet、SSD和FCN等。此外,該堆疊還提供庫元素,包括預定義和優化的CNN網路層實現,這是構建定制神經網路(DNN(深度神經網路)/CNN(卷積神經網路))所必需的。

機器學習元素還配合一系列豐富的支援加速功能的OpenCV功能,滿足電腦視覺處理要求。針對應用層開發,賽靈思支援工業級框架,包括面向機器學習的Caffe和面向電腦視覺的OpenVX。reVISION堆疊還包括了賽靈思和協力廠商提供的開發平臺以及各類感測器。

用reVISION的開發流程也很簡單,在SDSoC開發環境中,軟體工程師和系統工程師可以 reVISION硬體平臺為目標,並調用大量的加速就緒型電腦視覺庫進行開發,快速構建應用。

按照賽靈思的說法,採用傳統的RTL流程進行視覺處理開發,賽靈思的FPGA可以幫助用戶完成20%的工作,使用者需要解決剩餘的80%問題;而基於reVISION的開發則可以幫助用戶完成80%的工作量,用戶只需做剩下的20%即可,效率的提升十分顯著。

圖3,採用reVISION的軟體定義設計流程(圖片來源:賽靈思)

總之,一個為視頻處理專門優化的硬體架構Zynq Ultrascale+ MPSoC、一個簡單易用低門檻兒的SDSoC開發環境、一個資源豐富的reVISION堆疊,構成了嵌入式視覺開發“三件套”,它們可以幫助開發者大幅減少工作負荷、提升設計效率。一旦擁有,做個嵌入式視覺開發者,是不是件幸福的事兒?

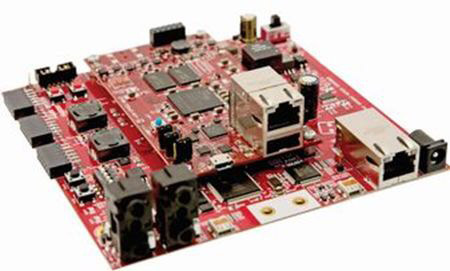

圖4,安富利推出的MicroZed嵌入式視覺開發套件,結合reVISION可以為開發者提供全面的嵌入式視覺設計開發支援

▲回頁首

|

|

|